# Utilization of Network-Based Multicomputers with ATM Technology in Digital Image Processing Applications

Antonio Garrido, Pedro Cuenca, Francisco Quiles, Teresa Olivares \* Universidad de Castilla - la Mancha Albacete, Spain

## Abstract

This paper presents a case of network-based multicomputer with high capacity networks based on ATM technology in digital image processing applications, providing solution proposals in case of loss of information. We propose to link the redundancy concept in digital image applications with the loss information concept in the network.

#### Keywords

ATM, Digital Image Processing, Loss Information, High Performance Distributed System, Network Based Multicomputer

### 1 Introduction

The adoption of a high speed network (like ATM) to overcome the bandwidth limitation introduced by traditional distributed systems based on traditional LAN technology [1][2]. Every day, is more frequent the use of distributed systems based on high-speed networks, also named Network-Based Multicomputers (NBM) or High Performance Distributed Systems (HPDS) [3]. There are two main families of NBM: message-passing and shared memory. The messagepassing system addapts better to the architecture of workstations clusters. In NBM, the main challenge is to minimize the impact of the network on the global performance [4]. This distributed systems differs substantially from traditional multicomputers, since are often heterogeneous and both the network and the nodes are shared with other users and the network can lose information.

Implementation of Digital Image Processing (DIP) techniques in parallel systems is more necessary as a consequence of the high processing capacity required [5] [6]. With the use of the new generation of high capacity networks based on ATM technology, more efficient systems where the communication network is no longer a bottle neck in the system are being obtained every day [7]. These networks allow distributed applications with highly reduced latency of transmission (and real-time applications), but flow control procedures based on discard packets [8] are incorporated so that under specific circumstances information losses may occur [8]. Some DIP parallel algorithms are observed to be liable to efficiently support information losses.

# 2 Loss information and redundancy in DIP Applications

In our work it is assumed that the network use a flow control based on cell discarding and therefore loss of information in the network may occur. The discarding mechanism proposed is very simple: once a cell is lost, the remaining cells of the same packet are dropped without verification. In case it does, two possibilities are considered: to ignore the loss of information assuming that the algorithm will undergo degradation; or to regenerate the information lost in destiny from previous information. In the first case, degradation suffered by the DIP algorithm when information loss occurs can be analyzed. In the second case, degradation suffered as a consequence of restoring some information which is likely to be somewhat different from the information received is also analyzed. In broad terms, we considered the possibility to transfer information deletion and restore techniques to a DIP distributed systems by studying system performance in terms of the rate of message losses and computation increase in processing nodes produced by information restore.

Also, using the information theory [11], it is possible to know the information of a message and if it is high, set a flag for the discard in congestion situation (CLP bit in ATM technology). It is the goal of the many compression techniques.

Data redundancy is a central issue in our work. It is a mathematically quantificable entity [10]. If  $n_1$  and  $n_2$  denote the number of information carrying units in two data sets that represent the same information, the relative data redundancy  $R_D$  of the

E-mail: antonio@info-ab.uclm.es

first data set can be defined as  $R_D = 1 - n_2/n_1$  and the information of a message with j cells I(message)can be defined as:

$$I(Message) = \sum_{j} \sum_{i} S_{ij} \cdot \log_2 \frac{1}{S_{ij}}$$

# 3 Virtual topologies over ATM network

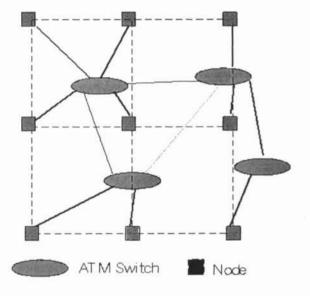

In our work the implementation of virtual topologies is analyzed starting from a high capacity network with ATM technology. To achieve this aim and using virtual circuit definition we design the desired topology which will subsequently allow us to implement algorithms designed for multicomputers using our distributed system. Figure 1 shows a 3x3 mesh virtual topology on an ATM network with four switches. Figure 2 shows in detail a portion of the mesh. Though we considered a mesh topology, it is possible to define other virtual topologies.

Figure 1: ATM physical network and virtual mesh

Virtual circuits are established in the initialization stage so that they can be available when the processors need to transmit data through them.

We use a modified version of NIST ATM simulator [12]. With this tool the user may create different physical topologies, create logical topologies, control components parameters, measure network activity and log data. Also, the ParDLXSIm simulator [13] has been used. ParDLXSim is a simulator of MIMD architecture, taking as reference the Paragon multicomputer. Thus, each node consists of two general purpose processors RISC DLX, one of them dedicated specifically to the communications tasks.

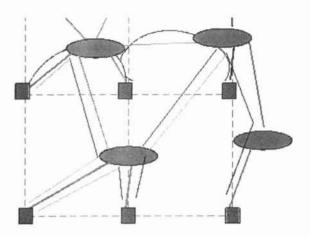

Figure 2: Detail of physical channel and virtual channels at network

### 4 Interface network - processor

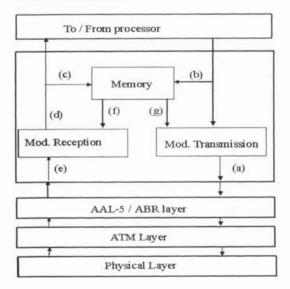

Each node has an interface that supervises the information exchange between network and processor. Several API have been proposed. In [14] a comparative study has been carried out. Figure 3 shows the interface structure.

Figure 3: Network-processor interface

The interface network processor contains four layers:

- Physical layer: Transport information across physical medium. It is the physical layer of the ATM architecture.

- ATM layer: It is the ATM layer of the ATM architecture. It mainly performs switching, rout-

ing and multiplexing.

- AAL layer: It is the AAL-5 layer of ATM architecture. It is responsible for adapting service information on the ATM stream. We use modified ABR (Available Bit Rate) mode in AAL-5.

- INP layer. It is a characteristic design. It is responsible for the analysis of the information sent by processors and for the regeneration of the information which does not arrive on time.

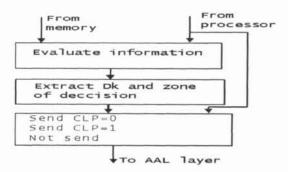

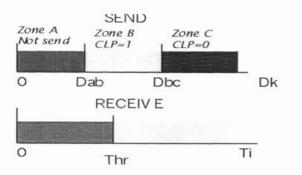

The INP design is one of the most important steps as it enables information regeneration in different forms. When a processor sends information the interface establishes (transmission module) whether it is sending a message with CLP desactivated (zone c), with CLP activated (zone b) or even if the message is not sent(zone a). If the message is the same as the previous one the right thing to do is not to send it to eliminate traffic in the network as it will be regenerated in destination by the receiver. Figure 4 shows in detail the transmission module and Figure 5 shows the three levels of decision

Figure 4: Transmission module

Figure 5: Levels of decision in INP

When the network information is received, it is first tested to check if it was the information expected, in which case it is directly passed to the processor. If it was not the information expected, it means that there has been loss of information in the network and therefore the information thought it should have been received is passed to the receiver. Moreover, with image sequences, the receiver will have available a timer so that in case a certain period of time is elapsed and no message has been received, the timer will analize the previous processes and simulate them. This situation is easy to implement as the interface module will be able to pass the last message or an average of the final N messages.

Two types of parameters can be considered to evaluate the limits of the previous levels (zones)  $(D_{ab}, D_{bc}$  and  $T_{hr}$ ). On the one side, data differentiation between two consecutive messages with the same destination and on the other the information supplied by a meesage with respect to the previous one. We can consider a delta function or a difference function. This second option provides higher resolution although a higher calculation capacity is required.

$$\sum_{i=0} n\delta[b_p(i) - b_{p-1}(i)]$$

## 5 Case of study

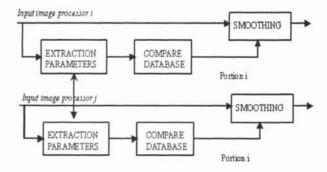

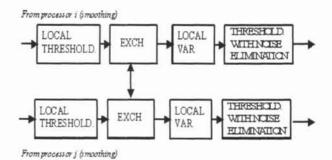

In this section, we show a example. We use a parallel algorithm for image segmentation [15]. We considered a real-time execution. Figures 6 and 7 show the outline of the algorithm.

Figure 6: Block diagram of the algorithm for the first step (smoothing)

Figure 7: Block diagram of the algorithm for the last stage)

In the first stage, a smoothing procedure based on self information is applied. In this stage, the processors exchange data with their neighbors. This information is statistical parameters and related data (figure 6). In the second stage, a bidimensional procedure with thresholding noise elimination is applied. In this stage, each processor is associated a part of the image. In this stage, a set of parameters is exchange between neighbouring processors and a broadcast pattern is involved. Finally, in the last stage, the processors exchange information with our neighbouring (figure 7). In this example, local and broadcast communication is used. Also, the length of the messages is smaller than an ATM cell (each message is inside the cell). If a cell is discarding, a complete message is lost.

Considering that the ATM presents background traffic, there is the possibility that some physical circuits can be overloaded and the flow control procedure may discard some cells. With the previous scheme traffic elimination in the network is obtained, which is proportional to *Dab* and *Dac* limits since Dab percent of the packages will not be sent. The effect of traffic elimination in the network is a degradation of the algorithm. In order to evaluate this degradation we have carried out simulations with and without loss of information, considering some objective fidelity criteria as root mean square (RMS) error between original and loss algorithm (4).

$$e(i) = \frac{1}{N^2} \sum \sum [[f(x, y, t) - f(x, y, t - 1)]^2] x^{1/2}$$

Moreover, we have considered any subjective fidelity criteria.

A second case for study is an algorithm that exchange great amounts of data. In this case the loss of a cell may be treated in two different ways. Either the cell lost is exclussively regenerated or the whole message is eliminated. In the first case the algorithm undergoes less degradation than in the second case, though results are more unpredictable. This type of algorithms require to be studied in many aspects, reason for which they will be analyzed in further studies.

#### 6 Future studies

Some studies related with the one just presented can be carried out. Firstly, the API module can be optimized and debugged, so that it uses the least possible resources.

The determination of common characteristics in algorithms which suffer information loss is very important to enable algorithm implementation. It is also important to establish criteria which allow the determination of adequate values for coefficients  $D_{ab}$ ,  $D_{ac}$  and  $T_{hr}$  for each type of algorithm.

#### 7 Acknowledgments

This work has been partially funded by the Spanish Ministry of Education (CICYT) under project PB092-519.

#### References

- G. Partidge, "Gb/s networks", Addison Wesley 1995

- [2] R. Hndel, M. Huber and S. Schrde "ATM Networks", Addison-Wesley 1995

- [3] Vila-Sallent, J. and Sole-Pareta, J., "High Performance Distributed Computing over ATM Networks: State of the Art", Technical report. University Politecnica de Catalunya, Spain.

- [4] R. Fatoohi and S. Weeratunga, "Performance evaluation of three distributed computing environments for scientific applications", Proceedings of Supercomputing'94, pp 400-409, 1995

- [5] A. Choudhary and S. Ranka, "Parallel processing for computer vision and image understanding", IEEE Computer, Vol 25, No 2, Feb 1992, pp 7-10

- [6] A.Chourdhary, J.N.Patel. "Parallel Architectures and Parallel Algorithmes for Integrated Vision Systems". Kluwer 1990.

- [7] C. Baransel, W. Dobosiewicz and P. Gburzynski, "Routing in multihop packet switching netgorks: the Gb/s challenge", IEEE Network, May 1995, pp 38-61.

- [8] R. Onvural, "Asynchronous transfer mode networks: Performance issues" Artech House 1995

- [9] H. Sheng and S. Li, "Spectral analysis of packet loss rate at a statistical multiplexer for multimedia services", IEEE Transactions on networking, vol 2, no 1 Feb 1994, pg 53-65

- [10] R. Gonzalez and R. Woods, "Digital Image Processing", Addison Wesley 1994

- [11] N. Abramson, "Teoria de la informacion y codificacion", Paraninfo 1986

- [12] N. Golmie, A. Koening and D. Su, "The NIST ATM Network Simulator", US. Department of Comerce, National Institute of Standards and Technology, Gaithersburg, MD 20899. Aug 1995

- [13] V. Valero, F. Cuartero, A. Garrido, F. Quiles, "A simulation tool of parallel architectures for digital image processing applications based on DLX processors". First IEEE International Conference on Image Proceesing, Washington 1995

- [14] M. Lin, D. Du, J. Thomas and J. Mac Donald, "Distributed network computing over local ATM networks", IEEE Journal on selectes areas in communications, pp 733-748, May 1995

- [15] A. Garrido, F. Quiles "A new algorithm for image segmentation based on self-information", IEEE/IASTED International Conference on Signal and Image Processing, Las Vegas, 1995